Intel/Altera Introduction to EP3C10E144I7N and Common Issues in FPGA Development

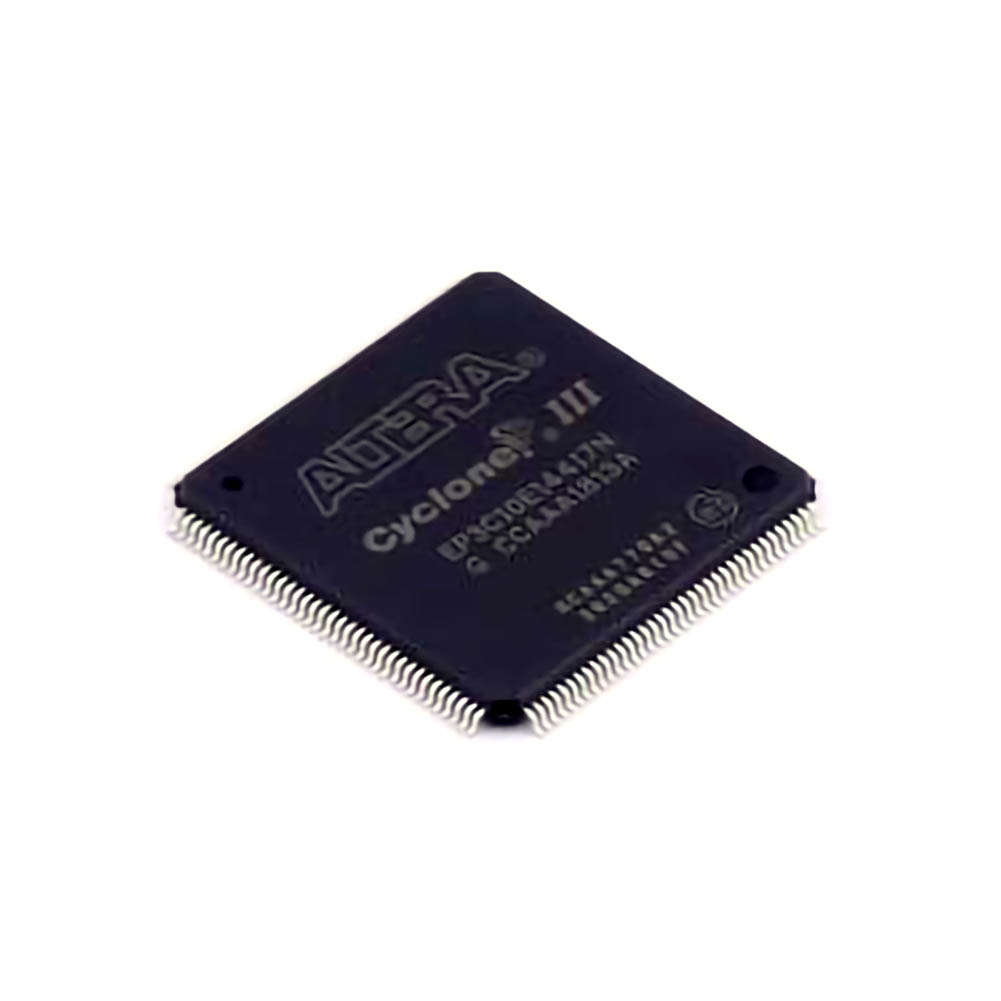

FPGAs ( Field Programmable Gate Array s) have become one of the cornerstones of modern electronic design, providing versatile and customizable hardware solutions. Among the many FPGA options available today, the EP3C10E144I7N, a member of the Intel (formerly Altera) Cyclone III family, stands out for its balance of performance, low Power consumption, and cost-efficiency. This makes it a popular choice in various applications, from Embedded systems to communication devices and automotive electronics.

However, like any complex piece of hardware, working with FPGAs, including the EP3C10E144I7N, comes with its own set of challenges. Engineers often face problems during design, simulation, and real-world implementation phases. Identifying and resolving these issues quickly can save time, prevent costly mistakes, and ensure the success of the final product.

This article addresses some of the most common problems associated with the EP3C10E144I7N FPGA, offering practical troubleshooting steps and solutions to streamline the design process.

1.1. Understanding EP3C10E144I7N FPGA

Before delving into troubleshooting, it is essential to have a basic understanding of the EP3C10E144I7N FPGA’s specifications and features. Manufactured by Intel, this FPGA is part of the Cyclone III family, known for its low power consumption and high-density logic resources. The "10" in EP3C10E144I7N refers to the device’s logic capacity (10,000 logic elements), and the "144" denotes the number of pins.

Some key specifications include:

Logic Elements: 10,000 logic elements

I/O Pins: 144

Programmable Logic Blocks: Flexible for both combinational and sequential logic design

Memory Blocks: Embedded memory (RAM) options for a variety of applications

Speed: Operates at high frequencies (depending on the design) while maintaining low power consumption.

This flexibility makes the EP3C10E144I7N ideal for a wide range of applications such as digital signal processing ( DSP ), communications, and industrial control systems. However, like all FPGAs, it requires careful design and management to avoid common issues.

1.2. Common Troubleshooting Areas for EP3C10E144I7N FPGA

Below are some of the most frequently encountered issues in FPGA development and troubleshooting for the EP3C10E144I7N:

Pin Assignment Issues: Incorrect pin mapping is one of the most common problems when working with FPGAs. If you misassign a signal to the wrong pin, it can lead to signal conflicts, improper connections, or a non-functional design.

Clock ing Problems: FPGAs rely on clocks to synchronize operations across different blocks. Incorrect clock setup or clock domain crossing can lead to Timing violations, causing the FPGA to operate incorrectly or even fail to initialize.

Power Supply Problems: Insufficient or unstable power delivery can cause the FPGA to malfunction, behave unpredictably, or fail to program properly.

Programming Issues: Failure during the FPGA programming process can be caused by a variety of factors, such as improper configuration files, incorrect voltage levels, or a faulty JTAG connection.

Design Constraints and Timing Violations: Ensuring that the FPGA design meets the timing constraints is crucial. Timing violations can lead to data corruption, signal degradation, and system instability.

Signal Integrity Issues: Noise, reflections, or crosstalk can affect high-speed signals in FPGA designs, leading to unpredictable behavior or degraded performance.

1.3. Overview of the Troubleshooting Approach

Effective troubleshooting of the EP3C10E144I7N FPGA involves a systematic approach. First, it’s essential to identify the specific problem or symptom that is occurring. Next, the issue should be isolated by checking various components and configurations, including the hardware connections, power supply, and clock setup. Lastly, corrective actions can be applied, and testing should be conducted to ensure that the solution is effective.

In the following sections, we will discuss the troubleshooting steps and solutions for common issues encountered during the development process for the EP3C10E144I7N FPGA.

Detailed Troubleshooting and Solutions for EP3C10E144I7N FPGA

Now that we have a solid understanding of the common issues that may arise while working with the EP3C10E144I7N FPGA, we can dive deeper into specific troubleshooting steps and solutions. The goal is to provide clear guidance on how to identify, diagnose, and resolve problems efficiently.

2.1. Pin Assignment Troubleshooting

Pin assignment errors are a frequent issue in FPGA design. Since the EP3C10E144I7N has a large number of I/O pins, misassignments can easily occur, leading to hardware malfunctions.

Symptoms:

Inconsistent or unexpected outputs

Lack of communication between devices (e.g., sensor readouts or signal transmission)

FPGA not responding to certain inputs

Troubleshooting Steps:

Check the Pin Assignment File: Start by reviewing your pin assignment file in the FPGA development environment. Ensure that each I/O signal is correctly mapped to the appropriate pin on the EP3C10E144I7N.

Cross-reference with Schematic: Compare your pin assignment file with the schematic of your design. It’s crucial that the signals align with the hardware design.

Check for Conflicts: Verify that no two signals are assigned to the same pin unless intentional. Conflicts can lead to erratic behavior or even short circuits.

Use Constraints for I/O Standards: Ensure that the I/O standards and voltage levels are compatible with the external hardware you are connecting to. Incorrect I/O standards can cause communication failures.

Solution:

Once you identify the misassigned pins, update the assignment in the development tool and recompile the design. Testing the design with a known good pinout will confirm the solution’s effectiveness.

2.2. Clocking and Timing Problems

Timing issues are prevalent in FPGA designs and are often caused by improper clock configurations, timing constraints, or issues with clock domain crossing.

Symptoms:

Timing violations during simulation or hardware testing

FPGA not initializing correctly

Slow or inconsistent signal processing

Troubleshooting Steps:

Check Clock Source: Ensure the clock signal is connected to the correct input pin and that the frequency is stable. Verify that external components such as oscillators or clock generators are functioning properly.

Verify Timing Constraints: Review the timing constraints in your project, including setup and hold times, and ensure they align with the FPGA’s maximum operating frequencies. Use the timing analyzer tools provided by the FPGA development environment to check for violations.

Check Clock Domain Crossing (CDC): When multiple clock domains are involved, ensure that proper synchronization is in place. Use synchronizers or FIFOs to handle asynchronous signals between clock domains.

Run Timing Analysis: After making changes, run the timing analysis again to ensure that no violations exist in the design.

Solution:

Once the root cause of the clocking or timing issue is identified, make the necessary adjustments in your clock setup, constraints, or clock domain crossing logic. Recompile the design and rerun the timing analysis to confirm that all timing constraints are met.

2.3. Power Supply and Voltage Issues

FPGAs like the EP3C10E144I7N are sensitive to power supply fluctuations. An inadequate or unstable power source can cause the FPGA to fail to initialize, behave unpredictably, or even be damaged.

Symptoms:

FPGA not programming or initializing

Unstable behavior, including random resets or failures

Overheating of the FPGA

Troubleshooting Steps:

Check Power Rails: Use a multimeter or oscilloscope to measure the power supply voltages. Ensure that the required voltages (e.g., 3.3V, 1.2V) are stable and within the specified tolerance levels.

Verify Power-up Sequence: Check the power-up sequence for the FPGA. Some FPGAs require specific power rails to come up in a particular order to avoid latch-up or damage.

Use Proper Decoupling Capacitors : Ensure that appropriate decoupling capacitor s are placed near the power pins to filter out noise and provide stability.

Test with Known Good Power Supply: If the problem persists, try powering the FPGA with a different, known good power supply to rule out issues with the current power source.

Solution:

After identifying any power-related issues, replace the faulty power supply or adjust the design to ensure proper power delivery. Adding additional decoupling capacitors or stabilizing the voltage rails may also solve the issue.

2.4. Programming and Configuration Issues

Programming the FPGA is a critical step in bringing your design to life. Any errors during the programming process can result in an unresponsive or improperly configured FPGA.

Symptoms:

FPGA not responding after programming

Configuration failure or programming timeout errors

Incorrect or corrupted design functionality

Troubleshooting Steps:

Check JTAG and Configuration Settings: Verify that the JTAG connection is functioning correctly and that the configuration settings are properly set in the development environment.

Reprogram the FPGA: Sometimes, programming errors may occur due to bad configurations. Try reprogramming the FPGA with a fresh bitstream file.

Test with Known Good Configuration File: If reprogramming doesn’t solve the problem, test the FPGA with a different configuration file known to work to rule out bitstream corruption.

Solution:

Once you identify and resolve the programming issue, reprogram the FPGA with the correct configuration and verify its functionality.

Conclusion

Troubleshooting the EP3C10E144I7N FPGA can seem daunting at first, but by systematically addressing common issues such as pin assignment errors, clocking problems, power supply instability, and programming failures, you can quickly identify and resolve the root cause. This guide provides a solid foundation for FPGA developers to confidently diagnose and fix issues that arise during design and development.

By following the steps outlined above and using the appropriate tools and methodologies, you can ensure that your EP3C10E144I7N FPGA designs are reliable, efficient, and optimized for performance. Happy debugging, and best of luck with your FPGA projects!

If you're looking for models of commonly used electronic components or more information about EP3C10E144I7N datasheets, compile all your procurement and CAD information in one place.

( Partnering with an electronic component supplier) sets your team up for success, ensuring that the design, production and procurement processes are streamlined and error-free. (Contact us) for free today.