In this article, we explore common troubleshooting methods and practical solutions for the EP4CE15F23I7N FPGA . Whether you're dealing with initialization issues, Communication problems, or performance optimization, this guide provides actionable steps to resolve various challenges and ensure your system operates smoothly.

EP4CE15F23I7N, FPGA troubleshooting, FPGA solutions, hardware troubleshooting, FPGA design, debugging FPGA, Altera FPGA, FPGA initialization, FPGA performance optimization, FPGA communication errors

Understanding EP4CE15F23I7N FPGA: Common Issues and Troubleshooting Steps

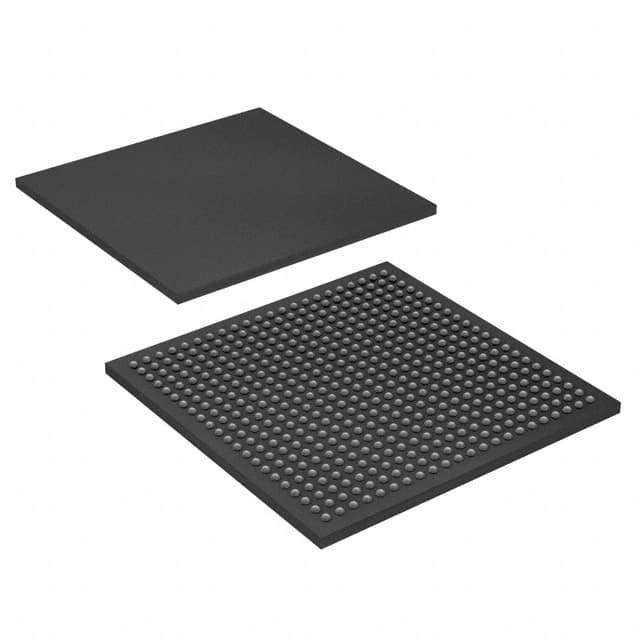

The Intel FPGAs/Altera EP4CE15F23I7N is part of the Cyclone IV family of Field-Programmable Gate Arrays (FPGAs) developed by Intel (formerly Altera). As an entry-level FPGA, the EP4CE15F23I7N is widely used for a range of applications, from communications and automotive systems to industrial automation and consumer electronics. While FPGAs offer flexibility and efficiency, they also come with their own set of challenges during development and deployment.

This guide aims to help you troubleshoot common issues you might encounter with the EP4CE15F23I7N FPGA and provide practical solutions to keep your design on track. Below are some of the most common problems you may face and the steps you can take to resolve them.

1. Power Supply Issues

Problem:

A faulty or unstable power supply is one of the most common issues when working with FPGAs, including the EP4CE15F23I7N. If the FPGA is not receiving sufficient or stable voltage, it may not power up correctly, leading to erratic behavior or no output at all.

Solution:

Ensure the power supply meets the voltage and current requirements for the EP4CE15F23I7N. The FPGA typically requires a 3.3V or 2.5V supply, but check the datasheet for specific voltage ranges for your configuration. It's also critical to verify that the power supply can deliver enough current to support the FPGA’s operational needs.

Use an oscilloscope to check for voltage fluctuations.

Make sure all ground connections are secure and properly routed.

If using external power regulators, verify they are functioning correctly.

Implement proper decoupling capacitor s close to the power pins to filter noise and ensure a stable power source.

2. Initialization Failures

Problem:

Initialization failures can occur if the FPGA fails to properly load the configuration file (bitstream) after power-up or reset. This often results in the FPGA not functioning as expected, even though there are no obvious hardware issues.

Solution:

Verify that the configuration file is correctly loaded into the FPGA. This can be done by checking the programming interface and ensuring the bitstream is correctly written to the FPGA's Memory .

Ensure that the initialization sequence is properly defined in your code. The reset signal must be asserted for a sufficient time to initialize all internal registers and logic blocks.

If using an external flash memory device to store the configuration file, check for faulty connections or corrupted data on the flash.

3. JTAG Communication Problems

Problem:

JTAG is commonly used for programming, debugging, and testing FPGAs. Communication errors over the JTAG interface can prevent you from uploading or debugging the FPGA’s configuration. Such errors can be caused by incorrect wiring, incompatible drivers, or Timing issues in the JTAG chain.

Solution:

Verify that all JTAG pins (TDI, TDO, TMS, TCK, and GND) are correctly connected. Double-check the connections with a multimeter or continuity tester.

Ensure that the FPGA’s JTAG interface is properly configured in your design and that the correct voltage levels are applied to the JTAG pins.

Check the JTAG cable and drivers on your computer. Reinstall or update the programming software if necessary.

If you're using a multi-device JTAG chain, ensure that the FPGA is correctly addressed and the devices are properly connected in sequence.

4. Clock ing Issues

Problem:

Clock-related issues are another common hurdle when working with FPGAs. These can include clock signal instability, incorrect frequency, or improper synchronization, which can lead to unpredictable behavior in your design.

Solution:

Confirm that the clock signal is present and stable. You can use an oscilloscope to check the clock waveform and ensure it meets the required specifications for frequency, duty cycle, and amplitude.

If using an external oscillator, check for any issues with the oscillator circuit, such as incorrect biasing or grounding.

Pay attention to clock domain crossing if your design involves multiple clock domains. Incorrect handling of these crossings can result in data corruption or glitches.

Consider using a PLL (Phase-Locked Loop) or DLL (Delay-Locked Loop) to generate stable, synchronized clock signals within the FPGA.

5. Configuration Memory Issues

Problem:

The EP4CE15F23I7N FPGA relies on external configuration memory, such as a flash memory, to store its configuration bitstream. Problems with the configuration memory can result in the FPGA not being able to load the design properly.

Solution:

Verify that the external configuration memory (e.g., SPI Flash) is correctly wired and powered.

Check for any issues with the configuration interface, such as SPI or Parallel, depending on your design.

If you’re using external memory for configuration, make sure that the memory chip is properly initialized and that the FPGA is reading it correctly.

Inspect the timing of the read/write operations between the FPGA and the external memory. Incorrect timing could cause issues during the configuration process.

6. Signal Integrity Problems

Problem:

Signal integrity issues such as reflections, crosstalk, or noise can cause unexpected behavior in FPGA designs, especially when high-speed signals are involved. These issues are particularly critical in communication interfaces like PCIe, Ethernet, and HDMI.

Solution:

Use proper PCB layout techniques, including controlled impedance traces and differential pairs for high-speed signals.

Ensure that the power and ground planes are continuous to minimize noise.

Implement signal termination where necessary to reduce reflections and ensure proper signal integrity.

Advanced Troubleshooting Techniques and Performance Optimization for EP4CE15F23I7N

While basic troubleshooting steps can often resolve common issues with the EP4CE15F23I7N FPGA, advanced troubleshooting techniques and performance optimization are necessary when dealing with more complex problems or when optimizing the FPGA for higher performance.

7. Timing Violations and Timing Analysis

Problem:

Timing violations are one of the most frustrating issues you can face during FPGA development. They occur when the FPGA design does not meet the required setup or hold times for internal signals, resulting in glitches, data corruption, or erratic behavior.

Solution:

Use Intel’s Quartus Prime software to run a static timing analysis. This will help you identify timing violations in your design and pinpoint areas where delays are too long or too short.

Pay attention to the constraints you define in your design. Ensure that clock constraints are correct and reflect the actual operating conditions of your design.

Optimize the logic design to reduce the number of critical paths. You can achieve this by using faster logic, reducing the depth of combinatorial logic, or utilizing pipeline stages to break up long paths.

Adjust the placement and routing of critical components to minimize delays.

8. Resource Utilization Issues

Problem:

FPGA designs can sometimes run out of resources, such as logic elements (LEs), memory blocks, or DSP blocks. This can lead to degraded performance, incorrect behavior, or even failure to fit the design onto the FPGA.

Solution:

Review the resource utilization report generated by Quartus Prime to identify which resources are being overused. This will help you identify potential bottlenecks.

If your design exceeds the available resources, consider optimizing your design by using more efficient algorithms, reducing the precision of data paths, or employing pipelining to reduce resource usage.

If possible, split your design across multiple FPGAs or use a larger FPGA that offers more resources.

9. Debugging with Signal Probes and Simulation

Problem:

One of the hardest challenges when troubleshooting FPGA designs is identifying the root cause of an issue. Without proper debugging tools, this process can be time-consuming and frustrating.

Solution:

Use Signal Tap Logic Analyzer within Quartus Prime for real-time signal probing. This tool allows you to capture and analyze internal FPGA signals during operation, helping you identify any unexpected behavior or logic errors.

In addition to real-time debugging, run functional simulations using ModelSim or other compatible simulators. Simulation will allow you to test your design in a controlled environment before deploying it to the actual FPGA hardware.

Use assertions and testbenches to simulate edge cases and ensure that all components of your design are functioning as expected.

10. Performance Optimization and Power Management

Problem:

As FPGA designs become more complex, power consumption and performance optimization become increasingly important. Poorly optimized designs may result in higher power consumption, slower performance, and thermal issues.

Solution:

Use the Power Analyzer tool in Quartus Prime to estimate the power consumption of your design. This can help you identify power-hungry components and make adjustments.

Optimize your design by using clock gating to reduce unnecessary clock switching, which can save power.

Consider using low-power modes or reducing the FPGA’s clock frequency if high performance is not critical for your application.

Use Dynamic Reconfiguration to change the FPGA’s functionality on the fly, minimizing resource usage and power consumption.

11. External Interfaces and Communication Protocols

Problem:

Communication issues often arise when interfacing the EP4CE15F23I7N FPGA with external devices, such as sensors, memory, or other processors. These problems may be due to incorrect timing, signal voltage levels, or incorrect protocol implementations.

Solution:

Verify the configuration and settings of the external devices you're interfacing with, ensuring that the communication protocol (e.g., I2C, SPI, UART, PCIe) is properly implemented and synchronized.

Use an oscilloscope or logic analyzer to check the signal integrity on the communication lines. Ensure that timing constraints are met and that the signals conform to the voltage levels required by both the FPGA and the external device.

If interfacing with high-speed communication protocols like PCIe or Ethernet, make sure the FPGA’s PHY (Physical Layer) interface is properly configured and the signaling rates are within the FPGA’s capabilities.

In conclusion, troubleshooting the EP4CE15F23I7N FPGA can be complex due to the wide variety of potential issues that can arise during development and deployment. However, by systematically addressing common problems such as power supply issues, initialization failures, JTAG communication problems, clocking issues, and signal integrity problems, you can identify and resolve these issues effectively. Additionally, employing advanced troubleshooting techniques and performance optimization strategies will ensure that your FPGA design runs smoothly and efficiently. With the right tools and approach, you can unlock the full potential of the EP4CE15F23I7N FPGA in your applications.

If you're looking for models of commonly used electronic components or more information about EP4CE15F23I7N datasheets, compile all your procurement and CAD information in one place.

(Partnering with an electronic component supplier) sets your team up for success, ensuring that the design, production and procurement processes are streamlined and error-free. (Contact us) for free today